Утвержден ГФКП.467444.004 ИП-ЛУ Модуль процессорный управления мультиплексными каналами **TA1-SMART** Инструкция пользователя ГФКП.467444.004 ИП

Взам. инв. № Инв. № дубл.

# Содержание

|                                                                                 | Стр. |

|---------------------------------------------------------------------------------|------|

| 1 НАЗНАЧЕНИЕ ИЗДЕЛИЯ, ОСОБЕННОСТИ ПОСТАВКИ, КОНСТРУКТИВНОЕ ИСПОЛНЕНИЕ           | 3    |

| 2 СОСТАВ И НАЗНАЧЕНИЕ ФУНКЦИОНАЛЬНЫХ УЗЛОВ                                      | 3    |

| 2.2.1 МОДУЛЬ РАЗОВЫХ КОМАНД                                                     | 5    |

| 3 ЭЛЕКТРИЧЕСКИЕ ХАРАКТЕРИСТИКИ                                                  | 6    |

| 4 ДОПОЛНИТЕЛЬНЫЕ ФУНКЦИИ                                                        | 7    |

| 5 НАЗНАЧЕНИЕ И ОПИСАНИЕ ФУНКЦИОНИРОВАНИЯ ТЕРМИНАЛА МУЛЬТИПЛЕКСНОГО КАН <i>А</i> | АЛА  |

|                                                                                 | 8    |

| 6 ПОДКЛЮЧЕНИЕ МОДУЛЯ ТА1-SMART К МУЛЬТИПЛЕКСНОМУ КАНАЛУ                         | 10   |

| 7 РАЗЪЕМЫ И ДЖАМПЕРЫ ИЗДЕЛИЯ                                                    |      |

| 7.1 Разъемы изделия                                                             |      |

| 8 ТА1-SMART ПРЕРЫВАНИЯ                                                          |      |

| 9 ТА1-SMART АДРЕСНОЕ ПРОСТРАНСТВО ВВОДА/ ВЫВОДА                                 | 18   |

| 10 BIOS SETUP                                                                   | 18   |

| 11 ПЕРЕНАПРАВЛЕНИЕ ВИДЕО ИНФОРМАЦИИ ЧЕРЕЗ СОМ ПОРТ                              | 19   |

| 12 ПЕРЕЗАПИСЬ ВІОЅ                                                              |      |

| 13 ОТВОД ТЕПЛА                                                                  | 19   |

| ПРИЛОЖЕНИЕ 1 ПРОЦЕССОРНЫЙ МОДУЛЬ MZF486-SMART. ТЕХНИЧЕСКОЕ ОПИСАНИЕ             | 20   |

| 1 НАЗНАЧЕНИЕ ИЗДЕЛИЯ, ОСОБЕННОСТИ ПОСТАВКИ                                      | 20   |

| 1.1 Состав и назначение функциональных узлов                                    | 20   |

| 1.2 ЭЛЕКТРИЧЕСКИЕ ХАРАКТЕРИСТИКИ                                                |      |

| 2 КРАТКОЕ ОПИСАНИЕ ПРОЦЕССОРА ZFX86                                             | 22   |

| 3 РАЗЪЕМЫ УСТРОЙСТВА                                                            | 22   |

| 3.1 УСТАНОВКА РЕЖИМОВ РАБОТЫ                                                    | 31   |

| 4 ПОДКЛЮЧЕНИЕ ОСНОВНЫХ ВНЕШНИХ УСТРОЙСТВ К МОДУЛЮ MZF486-SMART                  | 31   |

| 5 MZF486-SMART ПРЕРЫВАНИЯ                                                       | 34   |

| 6 MZF486- SMART АДРЕСНОЕ ПРОСТРАНСТВО ВВОДА/ ВЫВОДА                             | 34   |

| 7. ПОРЯДОК РАБОТЫ                                                               | 35   |

| 8 BIOS SETUP                                                                    | 35   |

| 9 РАБОТА С КОНСОЛЬЮ                                                             | 35   |

| 10 ПЕРЕЗАПИСЬ ВІОЅ                                                              | 36   |

| ПРИЛОЖЕНИЕ 2 ОПИСАНИЕ РАБОТЫ МУЛЬТИПЛЕКСНОГО КАНАЛА                             | 37   |

#### 1 Назначение изделия, особенности поставки, конструктивное исполнение

#### 1.1 Назначение изделия

Модуль процессорный управления мультиплексными каналами TA1-SMART, в дальнейшем тексте именуемый изделием, является PC-совместимым компьютером, построенном на процессоре PC-on-chip ZFX86. Имеет полную совместимость с PC программным обеспечением и любыми стандартными операционными системами, такими как DOS.. Обеспечивает интерфейсы со следующими устройствами:

- -накопителем на гибком диске

- -клавиатурой, мышью

- -двумя каналами RS-232 (COM1-COM2)

- -двумя резервированными мультиплексными каналами по ГОСТ Р 52070-2003

- -блоком разовых команд

#### 1.2 Особенности поставки

Условное обозначение изделия при его заказе и в конструкторской документации другого изделия, в котором оно применяется:

«Модуль процессорный управления мультиплексными каналами TA1-SMART(-XX)-A ГФКП.467444.004»,

где А – тип исполнения, принимающий значения:

С - коммерческое исполнение, приемка ОТК;

I - индустриальное исполнение, приемка ОТК, покрытие лаком;

М - исполнение «5», приемка Заказчика, покрытие лаком;

поле XX – поле, определяющее конструктивно-функциональное исполнение изделия

01 – исполнение изделия с одним резервированным мультиплексным каналом отсутствие поля – полное функциональное исполнение изделия:

02- исполнение изделия без мультиплексных каналов

Температурные диапазоны исполнений следующие:

повышенная температура среды предельная /рабочая для всех исполнений +85/+70°С; пониженная температура среды:

для исполнения C - минус 40/ минус 20°C, для исполнений I, M - минус 55/ минус 40°C.

# 1.3 Конструктивное исполнение

Изделие TA1-SMART выполнено в конструктиве PC-104. На верхнюю сторону устанавливается модуль MZF486-SMART, который крепится к несущей плате с помощью четырех винтов. Габаритный чертеж на TA1-SMART и MZF486-SMART приложен в поставочной документации.

### 2 Состав и назначение функциональных узлов

В состав изделия входит центральное процессорное устройство, выполненное на модуле процессорном мезонинном MZF486-SMART  $\Gamma\Phi$ KП. 467444.002, устройство управления, приемопередатчики RS-232, терминалы мультиплексного канала MK-1 и MK-2.

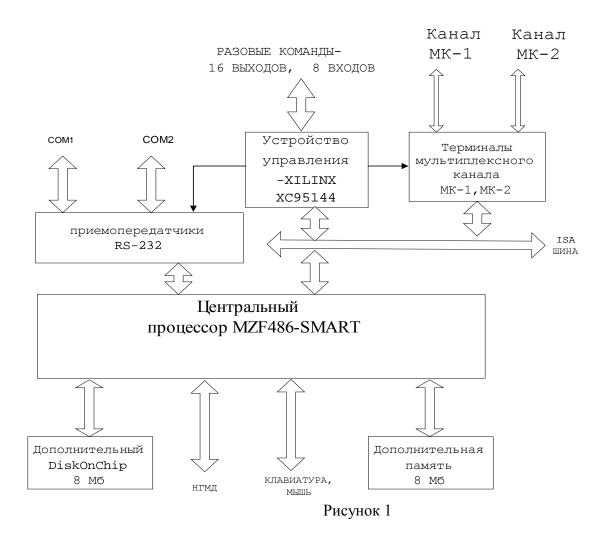

Структурная схема изделия приведена на рисунке 1.

Изделие состоит из функциональных узлов, назначение и характеристики которых приведены ниже.

# 2.1 Центральное процессорное устройство

Подробное описание центрального процессорного устройства приведено в приложении 1 технического описания MZF486-SMART ГФКП . 467444.001.

Основные технические характеристики и подключаемые интерфейсы следующие:

# 486+ CPU:

- -32 разрядное процессорное ядро Cyrix 586 FP DX, работающее на частоте 100, 66, 33 МГц,

- -8Кб КЭШ память первого уровня со сквозной и обратной записью,

- -сопроцессор режима с плавающей точкой.

# Последовательные порты:

-два 16550 совместимых RS232 последовательных порта( один порт перенастраиваемый на RS485/422)

-диапазон скорости не выше 115.2Кб.

#### Клавиатура и мышь:

-возможность подключения AT, PS/2 клавиатуры и PS/2 мыши.

### АТ совместимость:

- -DMA контроллеры типа 8237,

- -таймеры типа 8254,

- -контроллеры прерывания типа 8259А.

#### Двойной сторожевой таймер:

-программное управление первичным и вторичным таймером,

-выход 16 разрядного первичного сторожевого таймера может быть программно соединен с сигналами NMI, SMI, SCI или сигналом RESET (для немедленной перезагрузки системы),

-выход 8 разрядного вторичного таймера программно соединен с системным сигналом RESET.

# Управление энергопотреблением:

- -возможность использования таймера для задания интервала выдержки «неактивности» пользователя,

- -программный режим снижения активности.

# Шины расширения:

- 16 разрядная шина ISA PC/104.

#### DiskonCnip (FLASH носители):

- DiskOnChip Milenium объемом 8Мбайт.

### Динамическая память:

Синхронная SDRAM динамическая память объемом 16Мбайт.

# 2.2 Устройство управления

Устройство управления обеспечивает выдачу сигналов базового адреса устройству терминала мультиплексного канала, управление режимом работы COM2-RS232-RS485\422, содержит блок разовых команд. Блок разовых команд обеспечивает дискретный ввод-вывод -24 разрядов вводавывода:

- -выход →16 сигналов с открытым коллектором;

- -вход  $\to 8$  дискретных сигналов.

Устройство выполнено на микросхеме ХС95144.

# 2.2.1 Модуль разовых команд

В микросхеме программируемой логики Actel выполнен блок разовых команд. Контроллер протокола приема и передачи разовых команд осуществляет обслуживание до 8 входных и 16 выходных разовых команд. Для входных и выходных команд предусмотрен соединитель X5.

Базовый адрес устанавлен аппаратно в проекте Actel и равен адресу 150h. В области устройств ввода/вывода выделено 4 адреса. Адреса портов и функции регистров модуля при выполнении команд ввода/вывода приведены в таблице 2.

Таблица 2. Адреса устройств модуля разовых команд

| Адрес | Устройство модуля                        |                            |  |  |  |

|-------|------------------------------------------|----------------------------|--|--|--|

|       | при записи (OUT)                         | при чтении (IN)            |  |  |  |

| 150h  | 8 битный регистр выходов ОUT 0 - OUT 7   | 8 битный регистр состояния |  |  |  |

|       |                                          | входов IN 0 - IN 7         |  |  |  |

|       |                                          |                            |  |  |  |

| 151h  | 8 битный регистр выходов OUT 7 - OUT 15. |                            |  |  |  |

|       | Прим.1                                   |                            |  |  |  |

| 152h  |                                          | 8 битный регистр-защёлка   |  |  |  |

|       |                                          | выходов ОUТ 0 - ОUТ 7      |  |  |  |

| 153h  |                                          | 8 битный регистр-защёлка   |  |  |  |

|       |                                          | выходов OUT 7 - OUT 15.    |  |  |  |

Входные уровни модуля - TTL. Тип выхода - **открытый коллектор**. Запись логического нуля в регистр защелку выходов приводит к отпиранию выходных буферов и на их выходе образуется логический ноль, а запись логической единицы приводит к их запиранию и на выходе устанавливается третье состояние. По сигналу RESET регистры выходов устанавливаются в

логическую единицу. Установка подтягивающих резисторов выходных сигналов производится на устройствах, где эти сигналы используются. Входы подтянуты резисторами 10ком к 5 вольтам.

Состояние выходов 8 битных регистров можно прочитать по адресам согласно табл.2

# 2.2.2 Регистр режима приемопередатчика СОМ2

Управление выбором режима работы COM2 производится через четырех разрядный регистр управления. Назначение разрядов регистра управления представлено в таблице 3. Адрес для записи в данный регистр в пространстве ввода-вывода процессорного устройства-154h

Таблица 3

| разряд | НАЗНАЧЕНИЕ                                                           |

|--------|----------------------------------------------------------------------|

| 0      | СИГНАЛ ВЫБОРА RS-232 - RS-485/422 ДЛЯ ПРИЕМОПЕРЕДАТЧИКА COM2         |

|        | (ЛОГИЧЕСКИЙ "0" УСТАНАВЛИВАЕТ РЕЖИМ РАБОТЫ С RS-232, ЛОГИЧЕСКИЙ      |

|        | "1" УСТАНАВЛИВАЕТ РЕЖИМ РАБОТЫ С RS-485/422.)                        |

| 1      | СИГНАЛ ВЫБОРА РЕЖИМА РАБОТЫ RS-485/422 ДЛЯ ПРИЕМОПЕРЕДАТЧИКА         |

|        | СОМ2 (ЛОГИЧЕСКИЙ "0" - РАБОТАЕТ В ПОЛУ-ДУПЛЕКСНОМ РЕЖИМЕ,            |

|        | ЛОГИЧЕСКАЯ "1"-В ДУПЛЕКСНОМ РЕЖИМЕ)                                  |

|        | ПРИМЕЧАНИЕ: ПО СИГНАЛУ RESET СОСТОЯНИЕ РЕГИСТРА-FE. Разряды регистра |

|        | 2-7 не используются                                                  |

# 2.3 Терминал мультиплексного канала

Устройство содержит два независимых терминала мультиплексного канала.

Терминал мультиплексного канала предназначен для работы с резервированной магистралью по ГОСТ Р 52070-2003. Он содержит контроллер протокола, два приемопередатчика, два трансформатора гальванической развязки и защитные резисторы. Контроллер протокола выполнен на микросхеме APA450-PQ208 фирмы ACTEL, приемопередатчики фирмы Интеграл, тип трансформаторов гальванической развязки - ТИЛ6.

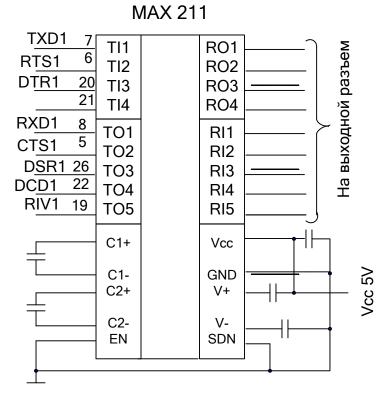

# 2.4 Приемопередатчики RS-232

Каналы RS-232 подключены в линию через микросхемы линейных драйверов MAX – 211, которые обеспечивают работу с уровнями выходных сигналов ± 9V. Второй канал может быть сконфигурирован, как на работу по RS-232, так и RS-485/422, путем управления разрядами 0,1 регистра управления. Назначение разрядов приведено в таблице 3.Для установки режима HALT-DUPLEX (режим работы RS-485) необходимо записать в регистр управления число -01h. Выходная линия подключается к контактам T+, T- разъема X16. При работе в режиме RS-485 необходимо установить джамперы на контакты 11-12, 13-14 для подключения подтягивающих резисторов к линиям T+ и T-. Для открытия выходных буферов RS-485 в режиме передачи в линию, выходной сигнал RTC должен находиться в логической единице. При переключении в режим приема из линии выходные буфера должны быть установлены в третье состояние путем установки выходного сигнала RTC в логический ноль.

Для установки режима FULL-DUPLEX (режим работы RS-422) необходимо записать в регистр управления число -03h. Выходная линия на передачу подключается к контактам T+, T-, а выходная линия на прием подключается к контактам R+, R-, разъема X16.

#### 3 Электрические характеристики

Электрические характеристики изделия приведены в таблице 4. Таблица 4

| Параметр                                    | Ед. изм. | Мин | Тип | Max |

|---------------------------------------------|----------|-----|-----|-----|

| Напряжение питания                          | В        | 4.5 | 5   | 5.5 |

| Мощность ядра процессора при частоте 100МГц | Вт       | -   | 0.5 | -   |

| Потребление платы при отсутствии передачи по   | мА         |      |      |      |

|------------------------------------------------|------------|------|------|------|

| мультиплексному каналу при частоте процессора: | MA         |      |      |      |

| ззмГц                                          |            | 820  |      |      |

| 100 MΓ <sub>Ц</sub>                            |            | 900  |      |      |

|                                                | 3.5 A      | 900  |      |      |

| Выходные токи:                                 | MA<br>Lal  |      | 10   |      |

| ISA шина                                       | Iol        |      | 10   |      |

|                                                | Ioh        |      | -8   |      |

| HEMI                                           | T 1        |      | 1.4  |      |

| НГМД                                           | Iol        |      | 14   |      |

|                                                | Ioh        |      | -14  |      |

|                                                |            |      |      |      |

| CDDAM                                          | T-1        |      | 0    |      |

| SDRAM                                          | Iol        |      | 8 -2 |      |

|                                                | Ioh        |      | -2   |      |

| ВВОД-ВЫВОД                                     | Iol        |      | 24   |      |

| Приемник                                       | 101        |      | 2 1  |      |

| Дифференциальное входное напряжение            | Vp-p       | 0,65 |      | 40   |

| Передатчик                                     | FF         | 3,00 |      |      |

| Дифференциальное выходное напряжение,          |            |      |      |      |

| измеренное в линии                             | Vp-p       | 6    | 6,5  |      |

| Время нарастания/спада сигнала                 | ns         | 100  | 150  | 300  |

| Требования по питанию                          |            |      |      |      |

| +5V                                            |            |      |      |      |

| пауза при частоте процессора 100МГц            | mA         |      |      | 1000 |

| majou npii matora npogeacopu roomi g           |            |      |      |      |

| * 50% времени передача по двум                 | mA         |      | 1200 | 1500 |

| мультиплексным каналам                         |            |      |      |      |

| * 100% времени передача по двум                | mA         |      | 1700 | 2000 |

| мультиплексным каналам                         |            |      |      |      |

| Временные параметры                            |            |      |      |      |

| • Задержка от запуска КШ до начала передачи    | μs         | 3    |      |      |

| • Контролируемая пауза до ОС в режиме КШ и МШ  | P          |      |      |      |

| (программируется)                              |            |      |      |      |

| • Контролируемая пауза в формате ОУ—ОУ         | μs         | 14,5 |      | 63,5 |

| (программируется)                              | μο         |      |      | ,    |

| (iipot paminipyoton)                           |            |      |      |      |

| • Задержка выдачи ответного слова ОУ           | μs         |      | 4.5  |      |

| Curtopinia Burga in Orbertion Choba Co         | "          |      |      |      |

| • Задержка формирования прерывания в           | μs         |      | 6    |      |

| конце задания для КШ и МШ                      | <b>M</b> 5 |      |      |      |

| кондо задания для кин и инн                    |            |      |      |      |

| • Контролируемая генерация в канале            | μs         | 800  |      |      |

| топтролируемая генерация в канале              | μδ         |      |      |      |

# 4 Дополнительные функции

# **Блок управления записью в BIOS:**

- 12кб специальная область памяти( BUR-BIOS Update ROM), предназначенная для обновления содержимого BIOS.

Программа BIOS:

-Phoenix PC BIOS-100% X86 совместимость

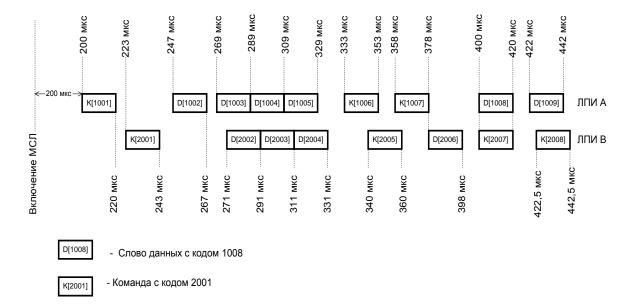

### 5 Назначение и описание функционирования терминала мультиплексного канала

Терминал мультиплексного канала предназначен для подключения модуля MZF486-SMART к резервированной магистрали ГОСТ Р 52070-2003 (MIL-STD-1553B). В зависимости от исполнения, модуль TA1-SMART содержит один или два устройства мультиплексного канала , каждый из которых реализует функции резервированного устройства интерфейса. Каждое устройство интерфейса способно функционировать в режиме контроллера шины (КШ), оконечного устройства(ОУ) или монитора шины(МШ), в соответствии с требованиями ГОСТ Р 52070-2003. Режим работы устройства определяется программно.

Поскольку модуль TA1-SMART может содержать один или два одинаковых устройства мультиплексного канала, в приложении 2 дано описание одного устройства мультиплексного канала.

# Подключение устройства контроллера протокола к шине ISA.

В качестве микросхемы, управляющей работой контроллера двух резервированных мультиплексных каналов, используется FPGA APA450-PQ208 фирмы Actel. Сигналы шины ISA подключаются к микросхеме APA450 через буфер IDTQS32X861, который ограничивает уровень принимаемых сигналов до величины 3.3V. Базовый адрес устройства для МК-1 и МК-2 задается аппаратно. Адрес МК1 -280h прерывание —IRQ10. Адрес МК2 -2A0h прерывание —IRQ11. Разряды SA4-SA1 используются для адресации регистров внутри МК1(МК2). Операции байтового чтения/записи не используются.

Назначение разрядов шины адреса ISA для устройства контроллера протокола приведено в Таблице 5.

Таблица 5

| SA9 | SA8       | SA7       | SA6      | SA5 | SA4                         | SA3 | SA2 | SA1 | SA0 |

|-----|-----------|-----------|----------|-----|-----------------------------|-----|-----|-----|-----|

|     |           |           |          |     |                             |     |     |     |     |

| Б   | базовый а | адрес 280 | ) или 2A | 0   | Адрес регистров контроллера |     | He  |     |     |

|     |           |           |          |     | протокола                   |     |     |     | исп |

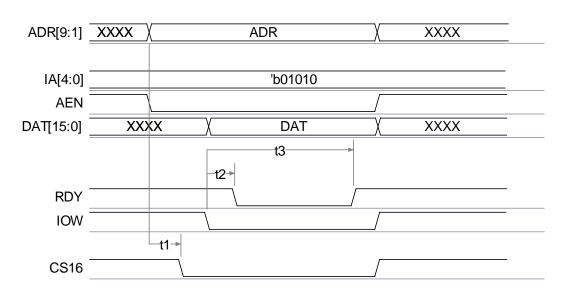

Для обмена управляющей информацией и данными между контроллера протокола и процессором используются циклы записи и чтения внешнего устройства. На рис.2 приведена временная диаграмма цикла записи и чтения.

а). Запись.

# б). Чтение.

Рис. 2

# 6 Подключение модуля TA1-SMART к мультиплексному каналу

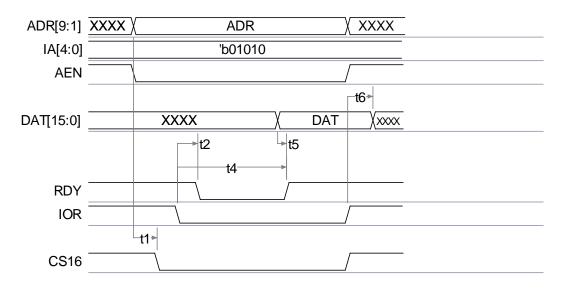

На рис. 3 показаны варианты подключения устройства TA1-SMART к линии передачи информации.

Рис 3

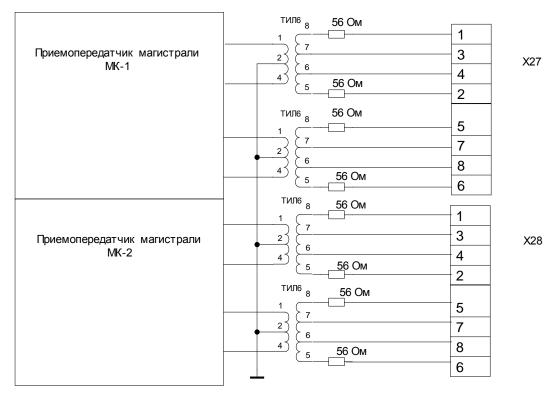

Схема подключения терминала мультиплексного канала к разъемам модуля TA1-SMART приведена на рис. 4.

Рис. 4. Подключение устройства к линии передачи информации.

#### 7 Разъемы и джамперы изделия

#### 7.1 Разъемы изделия

Разъемы устройства TA1-SMRART обеспечивают интерфейс к внешним устройствам, приведенным в таблице 6.

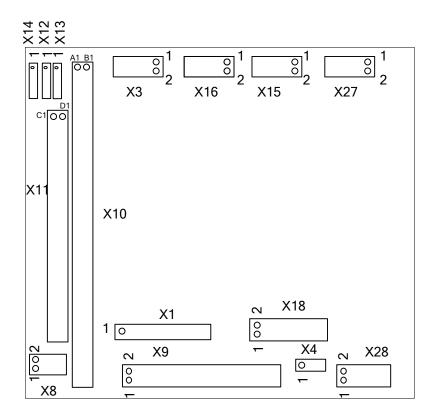

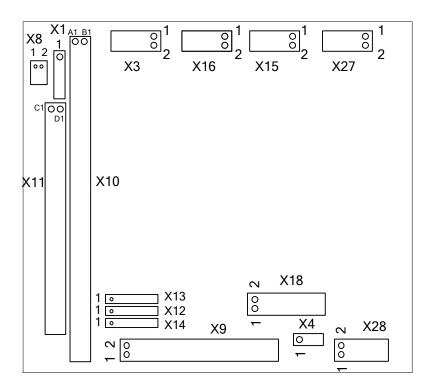

Условное изображение разъемов и джамперов устройства TA1-SMRART приведено на рисунке 2 для платы ниже версии 5 и на рисунке 3 для платы версии 5

Разъемы X1 и X18 предназначены для технологических целей на этапе изготовления и настройки устройства.

НГМД, подключаются с помощью стандартных шлейфных кабелей. Разъемы PC/104 сочленяются с соответствующими разъемами вышестоящих и нижестоящих плат. COM1 или COM2 могут подключается при работе на консоль (перенаправление видеоинформации через COM1 или COM2) к HOST компьютеру через нуль модемный кабель.

Рисунок 2 Расположение разъемов и джамперов на плате ниже версии 5

Рисунок 3 Расположение разъемов и джамперов на плате версии 6

Таблица 6

| Обозначение | Функциональное                     | Обозначение | Функциональное           |

|-------------|------------------------------------|-------------|--------------------------|

| разъема     | назначение                         | разъема     | назначение               |

| X1          | JTAG XILINX                        | X15         | COM1                     |

| X3          | Ввод, Вывод                        | X16         | COM2                     |

| X4          | Внешний разъем питания +5В         | X18         | Технологический разъем   |

| X8          | Клавиатура, Мышь                   | X27         | Мультиплексный канал МК1 |

| X9          | НГМД                               | X28         | Мультиплексный канал МК2 |

| X10         | РС/104 (64 контакта)               |             |                          |

| X11         | РС/104 (40 контактов)              |             |                          |

| X12,X13,X14 | Задание номера прерывания МК1, МК2 |             |                          |

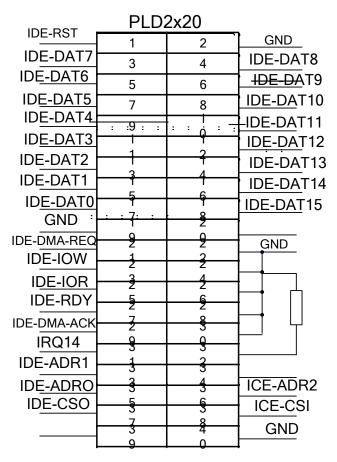

Подключение шины PC-104 производится через разъемы X10, X11. Обозначения выводов разъемов приведены в таблицах 7, 8.

Сигналы REFRESH и MASTER отсутствуют, на разъеме они подключены к логической "1".

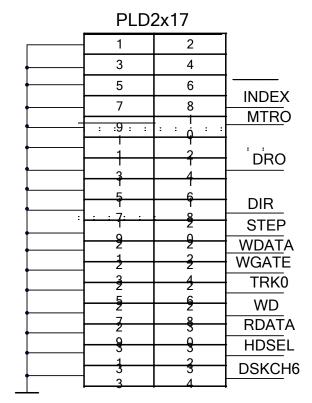

Подключение НГМД производится через разъемы X9. Обозначения сигналов разъема приведено в таблице 11.

Подключение COM1, 2 производится через разъемы X15, X16 соответственно. Обозначения сигналов разъема приведено в таблице 10, 11.

Подключение Мыши и клавиатуры производится через разъемы X8. Обозначения сигналов разъема приведено в таблице 12.

Подключение внешнего источника питания, если питание через ISA шину не подключено, производится через разъемы X4. Обозначения сигналов разъема приведено в таблице 13.

Подключение Ввода-Вывода производится через разъем X3. Обозначения сигналов разъема приведено в таблице 14.

Подключение терминала мультиплексного канала 1, 2 производится через разъем X27, X28. Обозначения сигналов разъема приведено в таблице 15,16.

Разъемы X12, X13, X14 предназначены для задания номера используемого прерывания контроллера МК1 и МК2. Разъемы X12 соединен с выходом прерывания контроллера МК1 и МК2. Разъемы X13 и X14 соединены с соответствующими линиями прерывания шины ISA. . Обозначения сигналов разъема приведено в таблице 17,18,19.

Устройство поставляется со следующими установленными прерываниями: контроллер MK1 - IRQ11, контроллера MK2 - IRQ10.

Таблипа 7 Разъем X10

| Ряд А | Обозн. сигнала | Ряд В | Обозн. сигнала |

|-------|----------------|-------|----------------|

| 1     | IOCHK          | 1     | GND            |

| 2     | SD7            | 2     | RESET          |

| 3     | SD6            | 3     | +5B            |

| 4     | SD5            | 4     | IRQ9           |

| 5     | SD4            | 5     | -              |

| 6     | SD3            | 6     | -              |

| 7     | SD2            | 7     | -              |

| 8     | SD1            | 8     | ZEROW          |

| 9     | SD0            | 9     | -              |

| 10    | RDY            | 10    | KEY            |

| 11    | AEN            | 11    | SMEMW          |

| 12    | SA19           | 12    | SMEMR          |

| 13    | SA18           | 13    | IOW            |

| 14    | SA17           | 14    | IOR            |

| Ряд А | Обозн. сигнала | Ряд В | Обозн. сигнала |

|-------|----------------|-------|----------------|

| 15    | SA16           | 15    | -              |

| 16    | SA15           | 16    | -              |

| 17    | SA14           | 17    | DACK1          |

| 18    | SA13           | 18    | DRQ1           |

| 19    | SA12           | 19    | REFRESH        |

| 20    | SA11           | 20    | SYSCLK         |

| 21    | SA10           | 21    | IRQ7           |

| 22    | SA9            | 22    | -              |

| 23    | SA8            | 23    | IRQ5           |

| 24    | SA7            | 24    | IRQ4           |

| 25    | SA6            | 25    | IRQ3           |

| 26    | SA5            | 26    | -              |

| 27    | SA4            | 27    | TC             |

| 28    | SA3            | 28    | BALE           |

| 29    | SA2            | 29    | +5B            |

| 30    | SA1            | 30    | OSC            |

| 31    | SA0            | 31    | GND            |

| 32    | GND            | 32    | GND            |

Таблица 8 Разъем X11

| Ряд С | Обозн. сигнала | Ряд <b>D</b> | Обозн. сигнала |

|-------|----------------|--------------|----------------|

| 1     | GND            | 1            | GND            |

| 2     | SBHE           | 2            | MCS16          |

| 3     | SA23           | 3            | IOCS16         |

| 4     | SA22           | 4            | IRQ10          |

| 5     | SA21           | 5            | IRQ11          |

| 6     | SA20           | 6            | IRQ12          |

| 7     | SA19           | 7            | IRQ15          |

| 8     | SA18           | 8            | IRQ14          |

| 9     | SA17           | 9            | -              |

| 10    | MEMR           | 10           | -              |

| 11    | MEMW           | 11           | DACK5          |

| 12    | SD8            | 12           | DRQ5           |

| 13    | SD9            | 13           | -              |

| 14    | SD10           | 14           | -              |

| 15    | SD11           | 15           | -              |

| 16    | SD12           | 16           | -              |

| 17    | SD13           | 17           | +5B            |

| 18    | SD14           | 18           | MASTER         |

| 19    | SD15           | 19           | GND            |

| 20    | -              | 20           | GND            |

Таблица 9 Разъем Х9

| № контакта | Обозначение сигнала | № контакта | Обозначение сигнала |

|------------|---------------------|------------|---------------------|

| 1          | GND                 | 18         | DIR                 |

| 2          | -                   | 19         | GND                 |

| 3          | GND                 | 20         | STEP                |

| 4          | -                   | 21         | GND                 |

| 5          | GND                 | 22         | WDATA               |

| 6          | -                   | 23         | GND                 |

| 7          | GND                 | 24         | WGATE               |

| 8          | INDEX               | 25         | GND                 |

| 9          | GND                 | 26         | TRACK0              |

| 10         | MOTON0              | 27         | GND                 |

| 11         | GND                 | 28         | WP                  |

| 12         | -                   | 29         | GND                 |

| 13         | GND                 | 30         | RDATA               |

| 14         | DRVSEL0             | 31         | GND                 |

| 15         | GND                 | 32         | HS                  |

| 16         | -                   | 33         | GND                 |

| 17         | GND                 | 34         | DSKCHG              |

Таблица 10 Разъем X15

| № контакта | Обозначение сигнала | № контакта | Обозначение сигнала |

|------------|---------------------|------------|---------------------|

| 1          | DCD                 | 6          | CTS                 |

| 2          | DSR                 | 7          | DTR                 |

| 3          | RXD                 | 8          | RIV                 |

| 4          | RTS                 | 9          | GND                 |

| 5          | TXD                 | 10         | -                   |

Таблица 11 Разъем Х16

| № контакта | Обозначение сигнала | № контакта | Обозначение сигнала |

|------------|---------------------|------------|---------------------|

| 1          | T+                  | 6          | CTS                 |

| 2          | T-                  | 7          | R+                  |

| 3          | RXD                 | 8          | R-                  |

| 4          | RTS                 | 9          | GND                 |

| 5          | TXD                 | 10         | -                   |

| 11         | T+                  | 12         | R1                  |

| 13         | T-                  | 14         | R2                  |

Таблица 12 Разъем X8

| № контакта | Обозначение сигнала | № контакта | Обозначение сигнала |

|------------|---------------------|------------|---------------------|

| 1          | KBCLK               | 5          | MBCLK               |

| 2          | KBDAT               | 6          | MBDAT               |

| 3          | +5B                 |            |                     |

| 4          | GND                 |            |                     |

Таблица 13 Разъем Х4

| № контакта | Обозначение сигнала |

|------------|---------------------|

| 1          | +5B                 |

| 2          | +5B                 |

| 3          | GND                 |

Таблица 14 Разъем X3

| № контакта | Обозначение сигнала | № контакта | Обозначение сигнала |

|------------|---------------------|------------|---------------------|

| 1          | ВВОД1               | 14         | вывод6              |

| 2          | ВВОД2               | 15         | вывод7              |

| 3          | ВВОД3               | 16         | вывод8              |

| 4          | ВВОД4               | 17         | вывод9              |

| 5          | ВВОД5               | 18         | ВЫВОД10             |

| 6          | ВВОД6               | 19         | ВЫВОД11             |

| 7          | ВВОД7               | 20         | ВЫВОД12             |

| 8          | ВВОД8               | 21         | ВВОД-ВЫВОД13        |

| 9          | ВЫВОД1              | 22         | ВВОД-ВЫВОД14        |

| 10         | ВЫВОД2              | 23         | ВВОД -ВЫВОД15       |

| 11         | ВЫВОД3              | 24         | ВВОД-ВЫВОД16        |

| 12         | ВЫВОД4              | 25         | ВВОД ПРЕРЫВАНИЯ     |

| 13         | ВЫВОД5              | 26         | ЗЕМЛЯ               |

Табл. 15 Разъем Х27

| № контакта | Обозначение сигнала | № контакта | Обозначение сигнала |

|------------|---------------------|------------|---------------------|

| 1          | 1SA+                | 5          | 1SB+                |

| 2          | 1SA                 | 6          | 1SB                 |

| 3          | 1LA+                | 7          | 1LB+                |

| 4          | 1LA                 | 8          | 1LB-                |

Табл. 16 Разъем Х28

| № контакта | Обозначение сигнала | № контакта | Обозначение сигнала |

|------------|---------------------|------------|---------------------|

| 1          | 2SA+                | 5          | 2SB+                |

| 2          | 2SA                 | 6          | 2SB                 |

| 3          | 2LA+                | 7          | 2LB+                |

| 4          | 2LA                 | 8          | 2LB-                |

Таблица 17 Разъем X13

| № контакта | Обозначение сигнала |

|------------|---------------------|

| 1          | IRQ5                |

| 2          | IRQ7                |

| 3          | IRQ9                |

| 4          | IRQ5                |

| 5          | IRQ7                |

| 6          | IRQ9                |

Таблица 18 Разъем X14

| № контакта | Обозначение сигнала |

|------------|---------------------|

| 1          | IRQ10               |

| 2          | IRQ11               |

| 3          | IRQ12               |

| 4          | IRQ10               |

| 5          | IRQ11               |

| 6          | IRQ12               |

Таблица 19 Разъем X12

| № контакта | Обозначение сигнала |

|------------|---------------------|

| 1          | INTA                |

| 2          | INTA                |

| 3          | INTA                |

| 4          | INTB                |

| 5          | INTB                |

| 6          | INTB                |

# 7.2 Джамперы изделия

С помощью установки перемычек на ответной части разъема X1, центрального процессора MZF486-SMART, производится установка частоты процессорного ядра. После необходимой установки следует перезагрузить OS. Положение перемычек и соответствующая этому положению частота процессорного ядра приведена в таблице 20.

Таблица 20

| Установка перемычек | Частота процессора |

|---------------------|--------------------|

| K.5-6, K.3-4        | 33 МГц             |

| K.3-4               | 66 МГц             |

| не установлены      | 100 МГц            |

Установка перемычки К.1-2 на ответной части разъема X1 разрешает выполнение инструкции BIOS из стандартной FLASH (режим boot ROM) или BUR. Если перемычка К.1-2 не установлена, изделие стартует нормально и выполняет инструкции BIOS, после чего передает управление загрузочному устройству. Если перемычка К.1-2 установлена, процессор выполняет BUR инструкции в перезаписи FLASH BIOS, используя COM1.

# 8 TA1-SMART прерывания

TA1-SMART прерывания представлены в таблице 21. Прерывания IRQ9-IRQ12 PCI шины можно переназначить в BIOS SETUP на прерывания IRQ9-IRQ12 шины ISA. Таблица 21

| Таолица 21 |                                                                        |

|------------|------------------------------------------------------------------------|

| N% IRQ     | ОПИСАНИЕ                                                               |

| 0          | Системный таймер ( нет возможности для других устройств )              |

| 1          | Клавиатура ( нет возможности для других устройств )                    |

| 2          | Второй каскадируемый контроллер прерываний (нет возможности для других |

|            | устройств)                                                             |

| 3          | COM2                                                                   |

| 4          | COM1                                                                   |

| 5          | Не назначен                                                            |

| 6          | НГМД ( нет возможности для других устройств )                          |

| 7          | Не назначен                                                            |

| 8          | Часы реального времени                                                 |

| 9          | Внешнее прерывание                                                     |

| 10         | МК1 (По умолчанию)                                                     |

| 11         | МК2 (По умолчанию)                                                     |

| 12         | Не назначен                                                            |

| 13         | Сопроцессор                                                            |

| 14         | Не назначен                                                            |

| 15         | Не назначен                                                            |

|            |                                                                        |

# 9 TA1-SMART адресное пространство ввода/ вывода

Адресное пространство ввода/ вывода представлено в таблице 22. Таблица 22

| І/О АДРЕС | НАЗНАЧЕНИЕ                             |

|-----------|----------------------------------------|

| 0000-000F | DMA КОНТРОЛЛЕР                         |

| 0020-0021 | Контроллер прерываний                  |

| 0040-0043 | Системный таймер                       |

| 0060-0060 | Клавиатура                             |

| 0064-0064 | Клавиатура                             |

| 0070-0071 | Системная CMOS/часы реального времени  |

| 0081-008F | DMA КОНТРОЛЛЕР                         |

| 00A0-00A1 | Контроллер прерываний                  |

| 00C0-00DF | DMA КОНТРОЛЛЕР                         |

| 00F0-00F1 | Сопроцессор                            |

| 280       | Базовый адрес МК-1                     |

| 150-151   | ВВОД-ВЫВОД                             |

| 154       | Регистр управление режимом работы СОМ2 |

| 2A0       | Базовый адрес МК-2                     |

| 02F8-02FF | COM2                                   |

| 03F0-03F5 | НГМД                                   |

| 03F8-03FF | COM1                                   |

# 10 BIOS SETUP

TA1-SMART BIOS имеет утилиту конфигурирования SETUP. Для входа в SETUP во время прохождения POST в нижней части экрана появляется надпись SETUP, после чего необходимо набрать F2. Детально порядок установок SETUP приведен в ZFX86 BIOS user manual supplement и PhoenixBIOS 4.0 REV. 6.0 . Первоначальные установки SETUP, загружаемые по умолчанию и записанные во FLASH BIOS, можно изменить с помощью программы ZEB.exe. При этом создается новый образ BIOS, который загружается во FLASH BIOS.

#### 11 Перенаправление видео информации через СОМ порт

Для многих задач таких, как конфигурация, запуск и отображение результатов работы рабочих и тестовых программ, имеющих небольшой объем видеоинформации, имеется возможность подключения устройства без видеокарты. В устройстве видеоинформация перенаправляется через последовательный порт СОМ1 или СОМ2 (консоль перенаправления).

Последовательный порт устройства соединен с удаленным терминалом через нульмодемный кабель. На удаленном терминале включена эмуляционная программа терминала, такая, например, как ТМ. Для установки работы по консоли необходимо установить одинаковые коммуникационные параметры в устройстве TA1-SMART и программе на удаленном терминале ТМ, например 115,2 Kbaud, N, 8, 1. Для работы по консоли в устройстве TA1-SMART необходимо войти в конфигурацию BIOS путем нажатия клавиши F2 во время загрузки.

Выбор Advanced меню и затем выбор Concole Redrection. В COM PORT ADRESS выбор COMA для COM1 или COMB для COM2. Если установлено Disabled, то перенаправление в COM порт производиться не будет. Выбор необходимой скорости производится в строке BAUD RATE. Для данного типа консоли выбор PC ANSI. Если необходимо продолжить перенаправление после завершения POST программы, необходимо установить в строке Continue C.R. after post:ON. Затем произвести запись изменений и перезагрузку устройства.

# **12 Перезапись BIOS**

ВІОЅ находится в отдельной перепрограммируемой FLASH памяти, поэтому его можно случайно стереть, когда в эту FLASH память записывают другие файлы. Для перезаписи ВІОЅ в процессоре TA1-SMART имеется устройство ВООТ-UP ROM (BUR), которое активизируется после включения питания. Программные утилиты обеспечивают восстановление системы путем загрузки ВІОЅ через СОМ1 порт. Компьютер, через который производится загрузка ВІОЅ, связан с TA1-SMART через нуль-модемный кабель. Распайка кабеля представлена в таблице 23. Для загрузки ВІОЅ необходимо подсоединить кабель к разъему X16 устройства TA1-SMART и к СОМ1 компьютера. На компьютере запустить batch файл TA1-SMART .bat, выполняющий следующие команды: Zftrm.exe loadbios.com ta1-smart.rom

После запуска программы на мониторе компьютера появится надпись, предлагающая установить джампер A23 и включить питание. На устройстве TA1-SMART необходимо установить джампер на контакты 1-2 разъема X1 и включить питание. После загрузки BIOS снимается джампер и включается питание. Визуально наблюдается запуск устройства со всеми необходимыми путями прохождения программы BIOS.

Таблица 23

| PC COM1(DB9) | МП-МКО (BLD2.0-10) |

|--------------|--------------------|

| 2 (RXD)      | 5 (TXD)            |

| 3 (TXD)      | 3 (RXD)            |

| 5 (GND)      | 9 (GND)            |

#### 13 Отвод тепла

Отвод тепла от платы осуществляется кондуктивным методом - путем отвода тепла от микросхем через внутренний тепловой слой на наружную металлизированную поверхность и далее на корпус блока. На центральное процессорное устройство укреплено на винтах теплоотводящая крышка из тонированного алюминия.

# Приложение 1 Процессорный модуль MZF486-SMART. Техническое описание

#### ГФКП 467444 001 ТО

#### Техническое описание

# 1 Назначение изделия, особенности поставки

Модуль MZF486-SMART является PC-совместимым компьютером, построенном на процессоре PC-on-chip ZFX86. Изделие имеет полную совместимость с PC программным обеспечением и любыми стандартными операционными системами такими, как LINUX, DOS, RTOS.

MZF86-SMART выполнен в конструктиве мезонинного модуля, для встраиваемых систем.

Условное обозначение изделия при заказе – «Процессорный модуль MZF486-SMART-А», где A – тип исполнения, принимающий значения:

С - исполнение с приемкой ОТК,

I – исполнение с приемкой ОТК, расширенным температурным диапазоном и покрытием лаком,

М - исполнение с приемкой Заказчика, расширенным температурным диапазоном и покрытием лаком.

Температурные диапазоны исполнений следующие:

повышенная температура среды предельная /рабочая

для всех исполнений +85/+70°C;

пониженная температура среды предельная /рабочая

для исполнения C минус 40/ минус 20°C, для исполнений I, M минус 55/ минус 40°C.

# 1.1 Состав и назначение функциональных узлов

#### 486+ CPU:

- -32 разрядное процессорное ядро Cyrix 586 FP DX, работающее на частоте 133, 100, 66 и 33 МГц,

- -8Кб КЭШ память первого уровня со сквозной и обратной записью,

- -сопроцессор режима с плавающей точкой.

Память:

- синхронная SDRAM динамическая память емкостью 16Мб.

#### Последовательные порты:

- два 16550 совместимых RS232 последовательных порта,

- диапазон скорости не выше 115.2Кб.

# Параллельные порты:

- один двунаправленный параллельный порт,

- возможность SPP, ECP и EPP режимов.

#### Клавиатура и мышь:

- возможность подключения AT, PS/2 клавиатуры и PS/2 мыши.

#### Контроллер НГМД:

- возможность подключения одного НГМД.

# Контроллер IDE

- один канал с возможностью подключения до двух устройств (master/ slave),

- PCI шина master с пакетной записью и чтением,

- режим ultra DMA, Multiword DMA и PIO (1-4).

# Контроллер USB

- два канала USB

#### АТ совместимость:

- DMA контроллеры типа 8237,

- таймеры типа 8254,

- контроллеры прерывания типа 8259А.

#### FLASH носители:

- DiskOnChip Milenium объемом 8Мбайт.

### Двойной сторожевой таймер:

- -программное управление первичным и вторичным таймером,

- -выход 16 разрядного первичного сторожевого таймера может быть программно соединен с сигналами NMI, SMI, SCI или сигналом RESET (для немедленной перезагрузки системы),

- -выход 8 разрядного вторичного таймера программно соединен с системным сигналом RESET.

### Управление энергопотреблением:

- -возможность использования таймера для задания интервала выдержки «неактивности» пользователя,

- -программный режим снижения активности.

# Шины расширения:

- 16 разрядная шина ISA PC/104,

- -32 разрядная (33МГц) РСІ шина, версия 2.1.

# 1.2 Электрические характеристики

Электрические характеристики изделия приведены в таблице 1.

Таблица 1

| Параметр                                  | 1    | Ед. | Мин  | Тип | Max  |

|-------------------------------------------|------|-----|------|-----|------|

|                                           | изм. |     |      |     |      |

| Напряжение питания                        | В    |     | 4.5  | 5   | 5.5  |

| Батарейный источник питания               | В    |     | 2.85 | 3   | 3.15 |

| Мощность ядра процессора при частоте      | Вт   |     | -    | 0.5 | -    |

| 100МГц                                    |      |     |      |     |      |

| Потребление от батарейки                  | мкА  |     |      | 1.5 | 2    |

| Потребление платы при частоте процессора: | мА   |     |      |     |      |

| 33 МГц                                    |      |     | 600  |     |      |

| 66 МГц                                    |      |     | 650  |     |      |

| 100 МГц                                   |      |     | 700  |     |      |

| Выходные токи:                            | мА   |     |      |     |      |

| ISA шина                                  | Iol  |     |      | 10  |      |

|                                           | Ioh  |     |      | -8  |      |

| НГМД, параллельный порт                   | Iol  |     |      | 14  |      |

|                                           | Ioh  |     |      | -14 |      |

| РСІ шина                                  | Iol  |     |      | 1.5 |      |

|                                           | Ioh  |     |      | -1  |      |

| IDE порт                                  | Iol  |     |      | 5   |      |

|                                           | Ioh  |     |      | -3  |      |

| SDRAM ВВОД-ВЫВОД                          | Iol  |     |      | 5   |      |

|                                           | Ioh  |     |      | -2  |      |

| Рабочая температура                       | °C   |     | -40  | -   | +70  |

| Предельная температура                    | °C   |     | -55  | -   | +85  |

# 1.3 Дополнительные функции

# Блок управления записью в BIOS:

- 12 кб специальная область памяти (BUR-BIOS Update ROM), предназначенная для обновления содержимого BIOS.

### Программа BIOS:

- Phoenix PC BIOS-100% X86 совместимость.

# 2 Краткое описание процессора ZFX86

Процессор ZFX86 является системой на кристалле CYRIX 586 FP DX с улучшенным 486/133-ядром. Архитектура, использующая 486/133-ядро с шинами ISA и PCI и развернутой системой ввода-вывода, является оптимальной для реализации контроллеров для встраиваемых систем. Ядро процессора имеет окружение (North Bridge и South Bridge), аналогичное тому, которое реализовано в процессорах класса Pentium, что обеспечивает высокопроизводительную работу системы.

North Bridge обеспечивает интерфейс центрального процессора с остальными ресурсами кристалла и организует циклы работы внутренней системной шины кристалла. Одной из основных задач North Bridge является управление SDRAM-памятью. North Bridge также осуществляет арбитраж шины PCI и определяет, какое устройство будет управлять этой шиной.

North Bridge поддерживает три внешних устройства мастера и два внутренних (это CPU и South Bridge ). North Bridge поддерживает режим управления энергопотреблением, формируемый модулем South Bridge.

Модуль South Bridge является улучшенным PCI-ISA мостом, обеспечивая ISA/AT-функционирование. South Bridge стыкуется с системным контроллером North Bridge по шине FRONT PCI и организует системный PCI- интерфейс, обеспечивая внешнюю шину PCI.

Модуль содержит IDE и USB контроллеры. IDE и USB контроллеры поддерживают шину mastering и стыкуются с быстродействующей PCI-шиной, обеспечивая высокопроизводительную работу системы со скоростной периферией.

North Bridge содержит интегрированную систему ввода-вывода:

- контроллер НГМД,

- два RS-232 порта,

- параллельный порт,

- -часы реального времени.

Подробное описание процессора приведено в ZFX86 DATA BOOK

## 3 Разъемы устройства

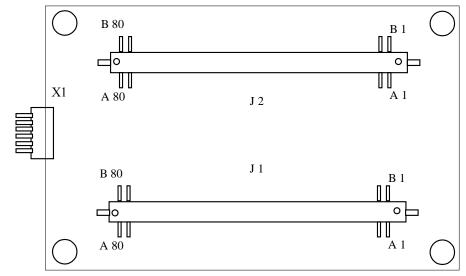

Разъемы MZF486-SMART обеспечивают интерфейс к внешним устройствам. Расположение разъемов приведено на рисунке 4 и рисунке 5.

Разъем J1, J2 предназначены для подключения MZF486-SMART к несущей плате. Обозначение сигналов приведено в таблице 2, 3. Обозначение сигналов по группам применения приведено в таблицах 4-14

Разъем X1 предназначен для установки частоты процессорного ядра и для установки режима загрузки BIOS. Обозначение сигналов приведено в таблице 3.

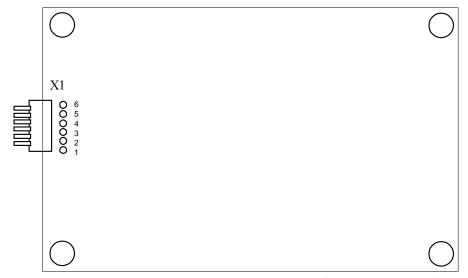

Рисунок 4 Расположение разъемов на плате (нижняя сторона)

Рисунок 5 Расположение разъемов на плате (верхняя сторона)

Таблица 2 Обозначение сигналов разъема Ј1

|          | блица 2 Обозначени |            |              | Т          |             |

|----------|--------------------|------------|--------------|------------|-------------|

| №        | Обозначение        | №          | Обозначение  | № контакта | Обозначение |

| контакта | сигнала            | контакта   | сигнала      |            | сигнала     |

| A1       | +5B                | A16        | SD6          | A31        | SA13        |

| A2       | RESDRV             | A17        | SD5          | A32        | SA12        |

| A3       | ISAERR             | A18        | SD4          | A33        | SA11        |

| A4       | SBHE               | A19        | SD3          | A34        | SA10        |

| A5       | MEMCS16            | A20        | SD2          | A35        | SA9         |

| A6       | IOCS16             | A21        | SD1          | A36        | SA8         |

| A7       | GND                | A22        | SD0          | A37        | SA7         |

| A8       | GND                | A23        | IOCHRDY      | A38        | SA6         |

| A9       | IOW                | A24        | AEN          | A39        | SA5         |

| A10      | IOR                | A25        | SA19         | A40        | SA4         |

| A11      | ZEROW              | A26        | SA18         | A41        | SA3         |

| A12      | ISACLK             | A27        | SA17         | A42        | SA2         |

| A13      | TC                 | A28        | SA16         | A43        | SA1         |

| A14      | ALE                | A29        | SA15         | A44        | SA0         |

| A15      | SD7                | A30        | SA14         | A45        | -           |

|          |                    |            |              |            |             |

| A46      | CLK14МГц           | A58        | +5B          | A70        |             |

| A47      | RESET_N            | A59        | +5B          | A71        | -           |

| A48      |                    | A60        | GND          | A72        | -           |

| A49      | GND                | A61        | GND          | A73        | -           |

| A50      | SMEMW              | A62        | GND          | A74        | PORT1 M     |

| A51      | SMEMR              | A63        | GND          | A75        | PORT1 P     |

| A52      | -                  | A64        |              | A76        | PORT2 M     |

| A53      | -                  | A65        |              | A77        | PORT2_P     |

| A54      | -                  | A66        |              | A78        | GND         |

| A55      | +5B                | A67        |              | A79        | MEMR        |

| A56      | +5B                | A68        |              | A80        | MEMW        |

| A57      | +5B                | A69        |              |            |             |

|          | <u> </u>           |            |              |            |             |

| B1       | +5B                | B16        | SA20         | B31        | TDO         |

| B2       | , 3B               | B17        | SA19         | B32        | IDE_DAT2    |

| B3       |                    | B18        | SA18         | B33        | IDE DAT6    |

| B4       |                    | B19        | SA17         | B34        | DACK5       |

| B5       |                    | B20        | SD8          | B35        | IDE DAT8    |

| B6       |                    | B21        | SD9          | B36        | IDE_DAT6    |

| B7       |                    | B22        | SD10         | B37        | IDE_DAT7    |

| B8       |                    | B23        | SD10         | B38        | IDE_DAT7    |

| B9       |                    | B24        | SD12         | B39        |             |

| B10      |                    | B25        | SD12<br>SD13 | B40        | IDE_DAT10   |

| B10      | DRQ5               | B25        | SD13         | B41        | IDE DAT11   |

| B12      | GND                | B27        | SD15         | B42        | IDE_DAT11   |

| B13      | -                  | B28        | TCK          | B43        | IDE DAT15   |

| B13      |                    | B29        | TDI          | B43        | IDE_DAT13   |

| B14      | SA21               | B29<br>B30 | TMS          | B45        | IDE_DA114   |

| DIS      | SAZI               | DSU        | CIVII        | D43        | -           |

| B46      |                    | B57        | IDE DMA DEO  | B70        | IDE DDV     |

|          | -                  |            | IDE_DMA_REQ  |            | IDE_RDY     |

| B47      | -                  | B58        | IDE_DAT4     | B71        | IDE_RST     |

| B48      |                    | B59        |              | B72        | O_CUR1      |

| №        | Обозначение | №        | Обозначение | № контакта | Обозначение |

|----------|-------------|----------|-------------|------------|-------------|

| контакта | сигнала     | контакта | сигнала     |            | сигнала     |

| B49      | -           | B60      |             | B73        | -           |

| B50      | -           | B61      | IDE_DAT0    | B74        | -           |

| B51      | -           | B62      | IDE_DAT1    | B75        | DRQ1        |

| B52      | -           | B63      | IDE_CS0     | B76        | DACK1       |

| B53      | -           | B64      | IDE_ADR0    | B77        | IDE_IOR     |

| B54      | IDE_DAT12   | B65      | IDE_ADR1    | B78        | -           |

| B55      | IDE_DAT9    | B66      | IDE_CS1     | B79        | IDE_IOW     |

| B56      | IDE_DMA_ACK | B67      | IDE_ADR2    | B80        | O_CUR2      |

|          |             | B68, B69 | -           |            |             |

Таблица 3 Обозначение сигналов разъема Ј2

| $N_{\underline{0}}$ | Обозначение | No       | Обозначение | № контакта | Обозначение |

|---------------------|-------------|----------|-------------|------------|-------------|

| контакта            | сигнала     | контакта | сигнала     |            | сигнала     |

| A1                  |             | A30      | -           | A59        |             |

| A2                  | -           | A31      | C_BE3       | A60        | C_BE1       |

| A3                  | -           | A32      | C_BE0       | A61        |             |

| A4                  |             | A33      | AD0         | A62        |             |

| A5                  |             | A34      | AD1         | A63        |             |

| A6                  |             | A35      | AD6         | A64        |             |

| A7                  |             | A36      | AD4         | A65        |             |

| A8                  |             | A37      | AD9         | A66        |             |

| A9                  |             | A38      | AD8         | A67        |             |

| A10                 |             | A39      | AD12        | A68        |             |

| A11                 |             | A40      | AD16        | A69        |             |

| A12                 |             | A41      | AD15        | A70        |             |

| A13                 |             | A42      | AD22        | A71        |             |

| A14                 |             | A43      | AD18        | A72        |             |

| A15                 |             | A44      | AD23        | A73        |             |

| A16                 |             | A45      | AD24        | A74        |             |

| A17                 |             | A46      | AD2         | A75        |             |

| A18                 |             | A47      | AD5         | A76        |             |

| A19                 |             | A48      | AD3         | A77        |             |

| A20                 |             | A49      | AD7         | A78        | IRQ11       |

| A21                 |             | A50      | AD11        | A79        | IRQ10       |

| A22                 |             | A51      | AD20        | A80        | IRQ09       |

| A23                 | KBDATA      | A52      | AD25        |            |             |

| A24                 | KBCLK       | A53      | AD30        |            |             |

| A25                 | MCLK        | A54      | AD29        |            |             |

| A26                 | MDATA       | A55      | FRAME       |            |             |

| A27                 | PCICLK      | A56      |             |            |             |

| A28                 |             | A57      |             |            |             |

| A29                 | -           | A58      |             |            |             |

| B1                  | DCD1        | B30      | MTR0        | B59        |             |

| B2                  | DSR1        | B31      | IRQ15       | B60        |             |

| В3                  | RXD1        | B32      | IRQ3        | B61        | LOCK        |

| B4                  | RTS1        | B33      | IRQ4        | B62        | STOP        |

| B5                  | TXD1        | B34      | IRQ5        | B63        | DEVSEL      |

| В6                  | CTS1        | B35      |             | B64        |             |

| B7                  | DTR1        | B36      | IRQ7        | B65        |             |

| №        | Обозначение | №        | Обозначение | № контакта | Обозначение |

|----------|-------------|----------|-------------|------------|-------------|

| контакта | сигнала     | контакта | сигнала     |            | сигнала     |

| B8       | RI1         | B37      | IRQ12       | B66        |             |

| B9       | DCD2        | B38      |             | B67        |             |

| B10      | DSR2        | B39      | PRST        | B68        |             |

| B11      | RXD2        | B40      | C_BE2       | B69        |             |

| B12      | RTS2        | B41      |             | B70        | AD10        |

| B13      | TXD2        | B42      |             | B71        | AD13        |

| B14      | CTS2        | B43      |             | B72        | AD14        |

| B15      | DTR2        | B44      |             | B73        | AD17        |

| B16      | RIV2        | B45      |             | B74        | AD19        |

| B17      | INDEX       | B46      | TRDY        | B75        | AD21        |

| B18      |             | B47      |             | B76        | AD26        |

| B19      | DSKCHG      | B48      | PERR        | B77        | AD27        |

| B20      | REQ1        | B49      | PAR         | B78        | AD28        |

| B21      | DIR         | B50      | SERR        | B79        | AD31        |

| B22      | STEP        | B51      | IRDY        | B80        |             |

| B23      | WDATA       | B52      | GNT0        |            |             |

| B24      | WGATE       | B53      | GNT1        |            |             |

| B25      | TRK0        | B54      | REQ0        |            |             |

| B26      | WP          | B55      | -           |            |             |

| B27      | RDATA       | B56      | -           |            |             |

| B28      | HDSEL       | B57      | SA23        |            |             |

| B29      | DRVSEL0     | B58      | SA22        |            |             |

Обозначения сигналов разъема J1, J2 для подключения шины ISA приведено в таблице 4.

Таблица 4 Обозначения сигналов для шины ISA

| № разъема | № контакта | Обозначение | № разъема | № контакта | Обозначение |

|-----------|------------|-------------|-----------|------------|-------------|

|           |            | сигнала     |           |            | сигнала     |

| J1        | A3         | IOCHK       | J1        | A39        | SA5         |

| J1        | A15        | SD7         | J1        | A40        | SA4         |

| J1        | A16        | SD6         | J1        | A41        | SA3         |

| J1        | A17        | SD5         | J1        | A42        | SA2         |

| J1        | A18        | SD4         | J1        | A43        | SA1         |

| J1        | A19        | SD3         | J1        | A44        | SA0         |

| J1        | A20        | SD2         | J1        | A11        | ZEROW       |

| J1        | A21        | SD1         | J1        | A50        | SMEMW       |

| J1        | A22        | SD0         | J1        | A51        | SMEMR       |

| J2        | B57        | SA23        | J1        | A9         | IOW         |

| J2        | B58        | SA22        | J1        | A10        | IOR         |

| J1        | B15        | SA21        | J1        | B76        | DACK1       |

| J1        | B16        | SA20        | J1        | B75        | DRQ1        |

| J1        | A25        | SA19        | J1        | A12        | SYSCLK      |

| J1        | A26        | SA18        | J2        | B36        | IRQ7        |

| J1        | A27        | SA17        | J2        | B34        | IRQ5        |

| J1        | A28        | SA16        | J2        | B33        | IRQ4        |

| J1        | A29        | SA15        | J2        | B32        | IRQ3        |

| J1        | A30        | SA14        | J2        | A80        | IRQ9        |

| J1        | A31        | SA13        | J2        | A79        | IRQ10       |

| J1        | A32        | SA12        | J2        | A78        | IRQ11       |

| J1        | A33        | SA11        | J2        | B37        | IRQ12       |

| № разъема | № контакта | Обозначение | № разъема | № контакта | Обозначение |

|-----------|------------|-------------|-----------|------------|-------------|

|           |            | сигнала     |           |            | сигнала     |

| J1        | A34        | SA10        | J2        | B31        | IRQ15       |

| J1        | A35        | SA9         | J2        | B38        | IRQ14       |

| J1        | A36        | SA8         | J1        | B17        | SA19        |

| J1        | A37        | SA7         | J1        | B18        | SA18        |

| J1        | A38        | SA6         | J1        | B19        | SA17        |

| J1        | A14        | BALE        | J1        | A13        | TC          |

| J1        | A5         | MEMCS16     | J1        | A2         | RESDRV      |

| J1        | A6         | IOCS16      | J1        | B34        | DACK5       |

| J1        | B20        | SD8         | J1        | B11        | DRQ5        |

| J1        | B21        | SD9         | J1        | A4         | SBHE        |

| J1        | B22        | SD10        | J1        | A46        | 14,3818МГц  |

| J1        | B23        | SD11        | J1        | A23        | IOHRDY      |

| J1        | B24        | SD12        | J1        | A24        | AEN         |

| J1        | B25        | SD13        | J1        | A79        | MEMR        |

| J1        | B26        | SD14        | J1        | A80        | MEMW        |

| J1        | B27        | SD15        |           |            |             |

Сигналы MASTER и REFRECH отсутствуют. Группа сигналов SA17-SA19 выведена на два разных места в разъеме J1

Обозначения сигналов разъема J1, J2 для подключения Hard диска приведено в таблице 5.

Таблица 5 Обозначения сигналов для Hard диска

| № разъема | № контакта | Обозначение | № разъема | №        | 2 Обозна      |

|-----------|------------|-------------|-----------|----------|---------------|

|           |            | сигнала     |           | контакта | чение сигнала |

| J1        | B71        | IDE_RST     | J1        | B42      | IDE_DAT13     |

| J1        | B61        | IDE_DAT0    | J1        | B44      | IDE_DAT14     |

| J1        | B62        | IDE_DAT1    | J1        | B43      | IDE_DAT15     |

| J1        | B32        | IDE_DAT2    | J1        | B57      | IDE_DMA_REQ   |

| J1        | B36        | IDE_DAT3    | J1        | B79      | IDE_IOW       |

| J1        | B58        | IDE_DAT4    | J1        | B77      | IDE_IOR       |

| J1        | B38        | IDE_DAT5    | J1        | B70      | IDE_RDY       |

| J1        | B33        | IDE_DAT6    | J1        | B56      | IDE_DMA_ACK   |

| J1        | B37        | IDE_DAT7    | J2        | B38      | IRQ14         |

| J1        | B35        | IDE_DAT8    | J1        | B65      | IDE_ADR1      |

| J1        | B55        | IDE_DAT9    | J1        | B64      | IDE_ADR0      |

| J1        | B40        | IDE_DAT10   | J1        | B67      | IDE_ADR2      |

| J1        | B41        | IDE_DAT11   | J1        | B63      | IDE_CS0       |

| J1        | B54        | IDE_DAT12   | J1        | B66      | IDE_CS1       |

|           |            |             |           |          |               |

Обозначения сигналов разъема J2 для подключения Floppy диска приведено в таблице 6.

Таблица 6 Обозначения сигналов для Floppy диска

| № разъема | № контакта | Обозначение | № разъема | №        | 3 Обозна      |

|-----------|------------|-------------|-----------|----------|---------------|

|           |            | сигнала     |           | контакта | чение сигнала |

| J2        | B17        | INDEX       | J2        | B21      | DIR           |

| J2        | B30        | MTR0        | J2        | B22      | STEP          |

| J2        | B29        | DRVSEL0     | J2        | B23      | WDATA         |

| J2        | B24        | WGATE       | J2        | B25      | TRACK0        |

| J2        | B26        | WP          | J2        | B27      | RDATA         |

| J2        | B28        | HDSEL       | J2        | B19      | DSKCHG        |

Обозначения сигналов разъема J2 для подключения COM1, 2 приведено в таблице 7, 8. Таблица 7 Обозначения сигналов для COM1

| № разъема | № контакта | Обозначение<br>сигнала | № разъема | №<br>контакта | Обозначение<br>сигнала |

|-----------|------------|------------------------|-----------|---------------|------------------------|

| J2        | B1         | DCD1                   | J2        | В6            | CTS1                   |

| J2        | B2         | DSR1                   | J2        | В7            | DTR1                   |

| J2        | В3         | RXD1                   | J2        | B8            | RIV1                   |

| J2        | B4         | RTS1                   | J2        | B5            | TXD1                   |

Таблица 8 Обозначения сигналов для СОМ2

| № разъема | № контакта | Обозначение | № разъема | №        | Обозначение |

|-----------|------------|-------------|-----------|----------|-------------|

|           |            | сигнала     |           | контакта | сигнала     |

| J2        | В9         | DCD2        | J2        | B14      | CTS2        |

| J2        | B10        | DSR2        | J2        | B15      | DTR2        |

| J2        | B11        | RXD2        | J2        | B16      | RIV2        |

| J2        | B12        | RTS2        | J2        | B13      | TXD2        |

Обозначения сигналов разъема J2 для подключения мыши и клавиатуры приведено в таблице 9.

Таблица 9 Обозначения сигналов для мыши и клавиатуры

| № разъема | № контакта | 1.1.1.4 Обозначение сигнала |

|-----------|------------|-----------------------------|

| J2        | A24        | KBCLK                       |

| J2        | A23        | KBDATA                      |

| J2        | A25        | MCLK                        |

| J2        | A26        | MDATA                       |

Обозначения сигналов разъема J1 для подключения USB 1, 2 портов приведено в таблице 10. Таблица 10 Обозначения сигналов USB 1, 2 портов

| № разъема | № контакта | Обозначение сигнала |

|-----------|------------|---------------------|

| J1        | A74        | PORT1_M             |

| J1        | A75        | PORT1_P             |

| J1        | A76        | PORT2_M             |

| J1        | A77        | PORT2_P             |

| J1        | B72        | O_CUR1              |

| J1        | B80        | O_CUR2              |

Обозначения сигналов разъема J2 для подключения PCI шины приведено в таблице 11. Таблица 11 Обозначения сигналов PCI шины

| № разъема | № контакта | Обозначение | № разъема | № контакта | Обозначение |

|-----------|------------|-------------|-----------|------------|-------------|

| _         |            | сигнала     | _         |            | сигнала     |

| J2        | A33        | AD0         | J2        | A54        | AD29        |

| J2        | A34        | AD01        | J2        | A53        | AD30        |

| J2        | A46        | AD02        | J2        | 319        | AD31        |

| J2        | A48        | AD03        | J2        | A80        | INTA        |

| J2        | A36        | AD04        | J2        | A79        | INTB        |

| J2        | A47        | AD05        | J2        | A78        | INTC        |

| J2        | A35        | AD06        | J2        | B37        | INTD        |

| J2        | A49        | AD07        | J2        | B39        | PRST        |

| J2        | A38        | AD08        | J2        | B49        | PAR         |

| J2        | A37        | AD09        | J2        | A32        | C_BE0       |

| J2        | 310        | AD10        | J2        | A60        | C_BE1       |

| J2        | A50        | AD11        | J2        | B40        | C_BE2       |

| J2        | A39        | AD12        | J2        | A31        | C_BE3       |

| J2        | B71        | AD13        | J2        | A27        | PCICLK      |

| J2        | B72        | AD14        | J2        | B62        | STOP        |

| J2        | A41        | AD15        | J2        | A55        | FRAME       |

| J2        | A40        | AD16        | J2        | B48        | PERR        |

| J2        | B73        | AD17        | J2        | B46        | TRDY        |

| J2        | A43        | AD18        | J2        | B51        | IRDY        |

| J2        | B74        | AD19        | J2        | B61        | LOCK        |

| J2        | A51        | AD20        | J2        | B63        | DEVSEL      |

| J2        | B75        | AD21        | J2        | B50        | SERR        |

| J2        | A42        | AD22        | J2        | B54        | REQ0        |

| J2        | A44        | AD23        | J2        | B20        | REQ1        |

| J2        | A45        | AD24        | J2        | B52        | GNT0        |

| J2        | A52        | AD25        | J2        | B53        | GNT1        |

| J2        | B76        | AD26        |           |            |             |

| J2        | B77        | AD27        |           |            |             |

| J2        | B78        | AD28        |           |            |             |

Обозначения сигналов разъема J2 для подключения параллельного порта приведено в таблице 12.

Таблица 12 Обозначения сигналов параллельного порта

| №       | №        | Обозначение | Nº      | № контакта | Обозначение |

|---------|----------|-------------|---------|------------|-------------|

| разъема | контакта | сигнала     | разъема |            | сигнала     |

| J2      | B67      | PD0         | J2      | B59        | PSLIN       |

| J2      | B68      | PD1         | J2      | B64        | PINIT       |

| J2      | B69      | PD2         | J2      | A58        | PERR        |

| J2      | B41      | PD3         | J2      | B44        | PACK        |

| J2      | B65      | PD4         | J2      | A56        | PBUSY       |

| J2      | B42      | PD5         | J2      | B45        | PPE         |

| J2      | A59      | PD6         | J2      | B43        | PSLCT       |

| J2      | A57      | PD7         | J2      | B66        | PSTB        |

| J2      | B35      | PAFD        |         |            |             |

Обозначения сигналов разъема J1, J2 для подключения дополнительной памяти DRAM приведено в таблице 13.

Таблица 13 Обозначения сигналов для дополнительной памяти DRAM

| № разъема | № контакта | Обозначение | № разъема | Nº       | Обозначение |

|-----------|------------|-------------|-----------|----------|-------------|

|           |            | сигнала     |           | контакта | сигнала     |

| J1        | 170        | D16         | J2        | 221      | R_CAS       |

| J1        | 167        | D17         | J2        | 222      | R_RAS       |

| J1        | 169        | D18         | J2        | 223      | R_CS0       |

| J1        | 168        | D19         | J2        | 224      | BA0         |

| J1        | 173        | D20         | J2        | 225      | BA1         |

| J1        | 172        | D21         | J2        | 227      | MR_A00      |

| J1        | 174        | D22         | J2        | 228      | MR_A01      |

| J1        | 171        | D23         | J2        | 229      | MR_A02      |

| J1        | 175        | D24         | J2        | 230      | MR_A03      |

| J1        | 177        | D25         | J2        | 237      | MR_A04      |

| J1        | 179        | D26         | J2        | 236      | MR_A05      |

| J2        | A16        | D27         | J2        | A75      | MR_A06      |

| J2        | A18        | D28         | J2        | A74      | MR_A07      |

| J2        | A21        | D29         | J2        | A73      | MR_A08      |

| J2        | A22        | D30         | J2        | A72      | MR_A09      |

| J2        | A20        | D31         | J2        | A66      | MR_A10      |

| J2        | B47        | R_CLK0      | J2        | A71      | MR_A11      |

| J2        | A11        | SDRAM_CS1   |           |          |             |

| J2        | B80        | R_WE        |           |          |             |

| J2        | A5         | SDRAM_CLK1  |           |          |             |

| J2        | A6         | SDRAM_DQM1  |           |          |             |

Обозначения сигналов разъема J1, J2 для подключения дополнительных сигналов приведено в таблице 14.

Таблица 14 Обозначения сигналов

| № разъема | № контакта | Обозначение | № разъема | Nº       | Обозначение |

|-----------|------------|-------------|-----------|----------|-------------|

|           |            | сигнала     |           | контакта | сигнала     |

| J1        | A47        | RESET_N     | J1        | B7       | IOCS0       |

| J1        | A48        | RTCBAT_3V   | J1        | B6       | IOCS1       |

| J1        | B2         | MEMCS2      | J1        | B5       | IOCS2       |

| J1        | B4         | MEMCS1      | J1        | B9       | IOCS3       |

| J1        | B28        | TCK         | J1        | B8       | PWM         |

| J1        | B29        | TDI         | J2        | A4       | SCL         |

| J1        | B30        | TMS         | J2        | A28      | SDA         |

| J1        | B31        | TDO         | J1        | B48      | GPIO4       |

Обозначения сигналов разъема J1, J2 для подключения напряжения питания приведено в таблице 15.

Таблица 15 Обозначения сигналов для подключения напряжения питания

| № разъема | № контакта | Обозначение | № разъема | No       | Обозначение |

|-----------|------------|-------------|-----------|----------|-------------|

|           |            | сигнала     |           | контакта | сигнала     |

| J1        | A64        | +3.3B       | J1        | A1       | +5B         |

| J1        | A65        | +3.3B       | J1        | A55      | +5B         |

| J1        | A66        | +3.3B       | J1        | A7       | GND         |

| J1        | A67        | +3.3B       | J1        | A8       | GND         |